免职声明:本网站为公益性网站,部分信息来自网络,如果涉及贵网站的知识产权,请及时反馈,我们承诺第一时间删除!

This website is a public welfare website, part of the information from the Internet, if it involves the intellectual property rights of your website, please timely feedback, we promise to delete the first time.

电话Tel: 19550540085: QQ号: 929496072 or 邮箱Email: Lng@vip.qq.com

摘要: 1概述 TLC1549系列是美国德州仪器公司生产的具有串行控制、连续逐次逼近型的模数转换器,它采用两个差分基准电压高阻输入和一个三态输出构成三线接口,其中三态输出分别为片选(CS低电平有效),输入/输出时钟(I/O CLOCK),数据输出(DATAOUT)。TLC1549引脚排..

|

1概述

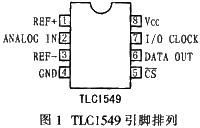

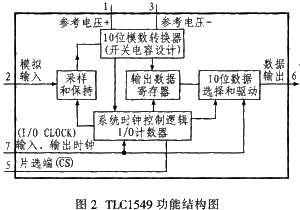

TLC1549系列是美国德州仪器公司生产的具有串行控制、连续逐次逼近型的模数转换器,它采用两个差分基准电压高阻输入和一个三态输出构成三线接口,其中三态输出分别为片选(CS低电平有效),输入/输出时钟(I/O CLOCK),数据输出(DATAOUT)。TLC1549引脚排列如图1所示。TLC1549能以串行方式送给单片机,其功能结构如图2所示。由于TLC1549采用CMOS工艺。内部具有自动采样保持、可按比例量程校准转换范围、抗噪声干扰功能,而且开关电容设计使在满刻度时总误差最大仅为±1 LSB(4.8 mV),因此可广泛应用于模拟量和数字量的转换电路。

TLC1549在工作温度范围内的极限参数:

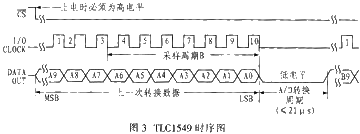

2 工作原理 TLC1549具有6种串行接口时序模式,这些模式是由I/O CLOCK周期和CS定义。根据TLC1549的功能结构和工作时序,其工作过程可分为3个阶段:模拟量采样、模拟量转换和数字量传输。图3所示为TLC1549的时序图。

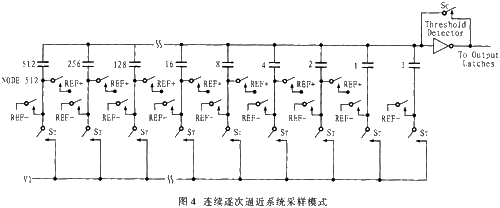

2.1 输入的模拟量采样 在第3个I/O CLOCK下降沿,输入模拟量开始采样,采样持续7个I/O CLOCK周期,采样值在第10个I/O CLOCK下降沿锁存。 2.2 输入的模拟量转换 对于连续逐次逼近型的模数转换器TLC1549,CMOS门限检测器通过检测一系列电容的充电电压决定A/D转换后的

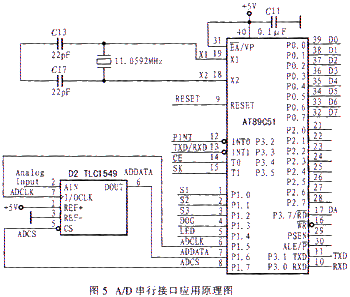

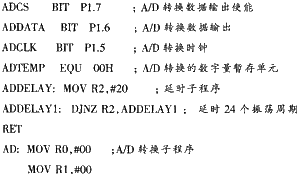

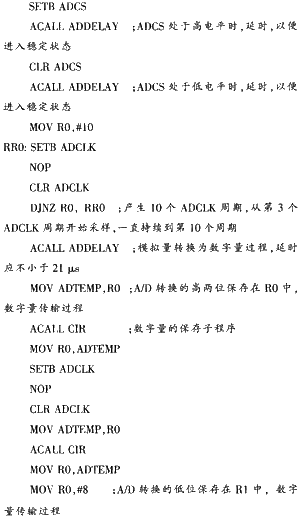

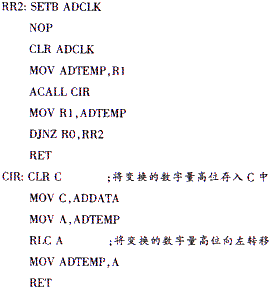

2.3 数字量的传输 当片选CS由低电平变为高时,I/O CLOCK禁止且A/D转换结果的三态串行输出DATA OUT处于高阻状态;当串行接口将CS拉至有效时,即CS由高变为低时,CS复位内部时钟,控制并使能DA-TA OUT和I/O CLOCK,允许I/O CLOCK工作并使DATA OUT脱离高阻状态。串行接口把输入/输出时钟序列供给I/O CLOCK并接收上一次转换结果。首先移出上一次转换结果数字量对应的最高位,下一个I/O CLOCK的下降沿驱动DATA OUT输出上一次转换结果数字量对应的次高位,第9个I/OCLOCK的下降沿将按次序驱动DATA OUT输出上一次转换结果数字量的最低位,第10个I/OCLOCK的下降沿,DATA OUT输出一个低电平,以便串行接口传输超过10个时钟;I/O CLOCK从主机串行接口接收长度在10~16个时钟的输入序列。 CS的下降沿,上一次转换的MSB出现在DATA OUT端。10位数字量通过DATA OUT发送到主机串行接口。为了开始传输,最少需要10个时钟脉冲,如果I/OCLOCK传送大于10个时钟,那么在第10个时钟的下降沿,内部逻辑把DATA OUT拉至低电平以确保其余位清零。在正常转换周期内,即规定的时间内CS端由高电平至低电平的跳变可以终止该周期,器件返回初始状态(输出数据寄存器的内容保持为上一次转换结果)。由于可能破坏输出数据,所以在接近转换完成时要小心防止CS拉至低电平。 3 实例应用及编程 实践中,某功能模块需将模拟电压转换为数字量,经过单片机处理后,储存在EEPROM中。利用P1.7作为片选端ADCS,P1.6作为数据输出端AD-DATA,P1.5作为时钟端ADCLK。图5所示为A/D串行接口应用原理图。

对于较大程序,应采用结构化程序设计,将整个程序按功能分成若干个模块,不同的模块完成不同的功能,这样可使整个应用系统程序结构清晰,易于调试和维护。以下给出了程序代码:

4 结束语 利用A/D串行输出设计不但提高了模数转换的精度,具有抗干扰性,而且节省了大量元件和印刷电路板的空间。该系统设计已经成功应用于工业现场控制系统的数据测量。 |